RISC

| RISC | ||

|---|---|---|

| ||

| Design paradigm vd | ||

| Dum | 1960-aj jaroj - nekonata/nuntempe | |

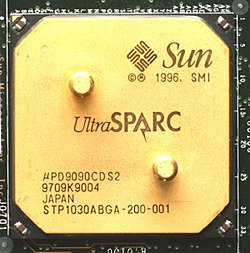

RISC (angle RISC: Reduced Instruction Set Computer, "reduktita instrukciara komputado") estas speco de procesora arĥitekturo kiu estas karakterizita per bazaj instrukcioj facile malkodigeblaj, nur kunmetitaj el simplaj instrukcioj.

Tiu strategio estis bone adaptita al la realigo de mikroprocesoroj. En la malfruaj 1980-aj jaroj kaj fruaj 1990-aj jaroj ĝi konkuris kun pli pezaj tradiciaj arĥitekturoj CISC (angle complex instruction-set computer, "kompleksa instrukciara komputado"). Efektive, la grandaj diferencoj en grandeco, malkoda tempo kaj ekzekuttempo estis malfavoraj al optimumoj de la tielnomita tipo "instrukcivico" (aperintaj en CDC 6600).

La apero de hibridaj arĥitekturoj kiel la Pentium Pro (CISC imitita de RISC[1]) ĉesigis, pro malapero de komparnormoj, ĉi tiun militon, kiu fariĝis multe pli merkata ol teĥnika ĉirkaŭ 1990, teĥnikoj evoluintaj ambaŭflanke kaj ĉiu komparante siajn procezojn al tiuj de la aliaj ses jarojn pli frue.

Referencoj

[redakti | redakti fonton]Vidu ankaŭ

[redakti | redakti fonton]Eksteraj ligiloj

[redakti | redakti fonton]Fonto

[redakti | redakti fonton]En tiu ĉi artikolo estas uzita traduko de teksto el la artikolo Processeur à jeu d'instructions réduit en la franca Vikipedio.